# 7SR11 and 7SR12

Applications Guide

# **Document Release History**

This document is issue 2012/02. The list of revisions up to and including this issue is:

| 2012/02 | AC auxiliary power supply added  |

|---------|----------------------------------|

| 2012/01 | Software Maintenance             |

| 2011/06 | Software Maintenance             |

| 2010/04 | Amendments following PLM review  |

| 2010/02 | Document reformat due to rebrand |

| 2009/09 | Revised Format and relay fascia. |

| 2009/04 | First Issue                      |

## **Software Revision History**

| 2012/01 | 7SR11 2436H80003 R2a-2a | Software Maintenance |

|---------|-------------------------|----------------------|

|         | 7SR12 2436H80004 R2a-2a |                      |

| 2011/06 | 7SR11 2436H80003 R2-2   | Software Maintenance |

|         | 7SR12 2436H80004 R2-2   |                      |

| 2009/04 | 2436H80003R1g-1c 7SR11  | First Release        |

|         | 2436H80004R1g-1c 7SR12  |                      |

The copyright and other intellectual property rights in this document, and in any model or article produced from it (and including any registered or unregistered design rights) are the property of Siemens Protection Devices Limited. No part of this document shall be reproduced or modified or stored in another form, in any data retrieval system, without the permission of Siemens Protection Devices Limited, nor shall any model or article be reproduced from this document unless Siemens Protection Devices Limited consent.

While the information and guidance given in this document is believed to be correct, no liability shall be accepted for any loss or damage caused by any error or omission, whether such error or omission is the result of negligence or any other cause. Any and all such liability is disclaimed.

# **Contents**

| Section 1 | : Common Functions                                                   |           |

|-----------|----------------------------------------------------------------------|-----------|

| 1.1       | Multiple Settings Groups                                             | 4         |

| 1.2       | Binary Inputs                                                        |           |

|           | 1.2.1 Alarm and Tripping Inputs                                      |           |

|           | 1.2.2 The Effects of Capacitance Current                             |           |

|           | 1.2.3 AC Rejection                                                   |           |

|           | 1.2.4 Use of Binary Inputs in control and tripping circuits          | 7         |

| 1.3       | Binary Outputs                                                       | 10        |

|           | LEDs.                                                                |           |

|           | 2: Protection Functions                                              |           |

|           | Time delayed overcurrent (51/51G/51N)                                |           |

| ۷.۱       | 2.1.1 Selection of Overcurrent Characteristics                       |           |

|           | 2.1.2 Reset Delay                                                    |           |

| 2.2       |                                                                      |           |

| 2.2       | Voltage dependent overcurrent (51V)  Cold Load Settings (51c)        | 14<br>1.1 |

|           |                                                                      |           |

| 2.4       |                                                                      |           |

| 0.5       | 2.4.1 Blocked Overcurrent Protection Schemes                         | 15        |

|           | \                                                                    |           |

| 2.6       | Directional Protection (67)                                          |           |

|           | 2.6.1 2 Out of 3 Logic                                               |           |

| 2.7       | Directional Earth-Fault (50/51G, 50/51N, 50/51SEF)                   |           |

|           | 2.7.1 Compensated Coil Earthing Networks                             |           |

|           | 2.7.2 Isolated Networks                                              |           |

|           | 2.7.3 Minimum Polarising Voltage                                     | 23        |

| 2.8       |                                                                      |           |

|           | Negative Phase Sequence Overcurrent (46NPS)                          |           |

|           | Undercurrent (37)                                                    |           |

| 2.11      | 1 Thermal Overload (49)                                              | 26        |

| 2.12      | 2 Under/Over Voltage Protection (27/59)                              | 27        |

|           | 3 Neutral Overvoltage (59N)                                          |           |

|           | 2.13.1 Application with Capacitor Cone Units                         | 29        |

|           | 2.13.2 Derived NVD Voltage                                           |           |

| 2.14      | Negative Phase Sequence Overvoltage (47)                             | 29        |

|           | 5 Under/Over Frequency (81)                                          |           |

|           | 3: CT Requirements                                                   |           |

| 3 1       | CT Requirements for Overcurrent and Earth Fault Protection           | 31        |

| 0.1       | 3.1.1 Overcurrent Protection CTs                                     | 31        |

|           | 3.1.2 Earth Fault Protection CTs                                     | 31        |

| 3.2       | CT Requirements for High Impedance Restricted Earth Fault Protection | 31        |

|           | E: Control Functions                                                 |           |

| 4.1       |                                                                      |           |

| 4.1       | 4.1.1 Auto-Reclose Example 1                                         |           |

|           | 4.1.2 Auto-Reclose Example 2 (Use of Quicklogic with AR)             |           |

| 4.0       | 4.1.2 Adio-reclose Example 2 (USE of Quicklogic With AR)             | 34        |

| 4.2       | Quick Logic Applications                                             |           |

| 04: 5     | 4.2.1 Auto-Changeover Scheme Example                                 |           |

|           | Supervision Functions                                                |           |

| 5.1       | Circuit-Breaker Fail (50BF)                                          |           |

|           | 5.1.1 Settings Guidelines                                            |           |

| 5.2       | Current Transformer Supervision                                      |           |

| 5.3       | Voltage Transformer Supervision (60VTS)                              |           |

| 5.4       | Trip/Close Circuit Supervision (74T/CCS)                             |           |

|           | 5.4.1 Trip Circuit Supervision Connections                           |           |

|           | 5.4.2 Close Circuit Supervision Connections                          |           |

| 5.5       | Inrush Detector (81HBL2)                                             |           |

| 5.6       | Broken Conductor / Load Imbalance (46BC)                             | 42        |

|           | 5.6.1 Broken Conductor example                                       | 43        |

| 5.7       | Circuit-Breaker Maintenance                                          | 4.3       |

# **List of Figures**

|              | Example Use of Alternative Settings Groups                                        |    |

|--------------|-----------------------------------------------------------------------------------|----|

| Figure 1.2-2 | 2 Example of Transformer Alarm and Trip Wiring                                    | 5  |

| Figure 1.2-3 | Binary Input Configurations Providing Compliance with EATS 48-4 Classes ESI 1 and |    |

| · ·          | ESI 2                                                                             | 9  |

| Figure 1.4-1 | LED configuration via the LED Matrix tab                                          | 10 |

|              | LED configuration via the Settings \ OUTPUT CONFIG \ LED CONFIG menu              |    |

|              | I IEC NI Curve with Time Multiplier and Follower DTL Applied                      |    |

|              | 2 IEC NI Curve with Minimum Operate Time Setting Applied                          |    |

|              | B Reset Delay                                                                     |    |

|              | Form of DTL Operate Characteristic                                                |    |

|              | 5 Blocking Scheme Using Instantaneous Overcurrent Elements                        |    |

|              | S Sensitive Earth Fault Protection Application                                    |    |

|              | 7 Directional Characteristics                                                     |    |

|              | B Phase Fault Angles                                                              |    |

|              | Application of Directional Overcurrent Protection                                 |    |

|              | Earth fault current distribution in Compensated network                           |    |

| Figure 2.7-1 | Earth fault current distribution in compensated network                           |    |

|              | 2 Earth fault current direction in compensated network                            |    |

|              | 3 Adjustment of Characteristic Angle                                              |    |

|              | Cosine component of current                                                       |    |

|              | Earth fault current in isolated network                                           |    |

|              | Balanced and Restricted Earth-fault protection of Transformers                    |    |

|              | 2 Composite Overcurrent and Restricted Earth-fault Protection                     |    |

|              | -3 Thermal Overload Heating and Cooling Characteristic                            |    |

|              | -4 NVD Application                                                                |    |

|              | -5 NVD Protection Connections                                                     |    |

|              | -1 Load Shedding Scheme Using Under-Frequency Elements                            |    |

|              | Sequence Co-ordination                                                            |    |

|              | 2 Example of Logic Application                                                    |    |

|              | B Example Use of Quick Logic                                                      |    |

|              | Circuit Breaker Fail                                                              |    |

|              | 2 Single Stage Circuit Breaker Fail Timing                                        |    |

|              | 3 Two Stage Circuit Breaker Fail Timing                                           |    |

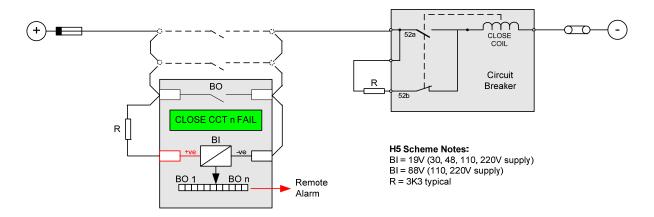

| Figure 5.4-4 | Frip Circuit Supervision Scheme 1 (H5)                                            | 40 |

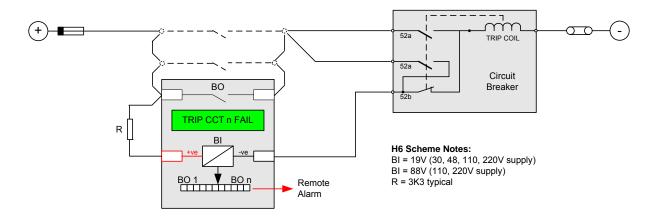

| Figure 5.4-5 | 5 Trip Circuit Supervision Scheme 2 (H6)                                          | 41 |

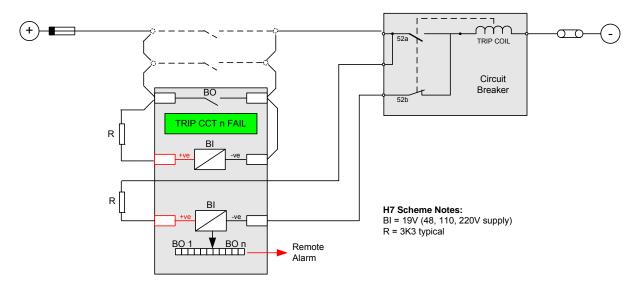

| Figure 5.4-6 | 3 Trip Circuit Supervision Scheme 3 (H7)                                          | 41 |

|              |                                                                                   |    |

|              |                                                                                   |    |

|              |                                                                                   |    |

|              |                                                                                   |    |

| 1:-4-5       | Tables                                                                            |    |

| LIST OF      | Tables                                                                            |    |

| T-51- 0 4    | Application of IDNATI. Observatoristics                                           | 40 |

| Table 2-1    | Application of IDMTL Characteristics                                              | 13 |

| Table 5-1    | Determination of VT Failure (1 or 2 Phases)                                       |    |

| Table 5-2    | Determination of VT Failure (1 or 2 Phases)                                       |    |

| Table 5-3    | Determination of VT Failure (3 Phases)                                            |    |

| Table 5-4    | Magnetic Inrush Bias                                                              | 42 |

## **Section 1: Common Functions**

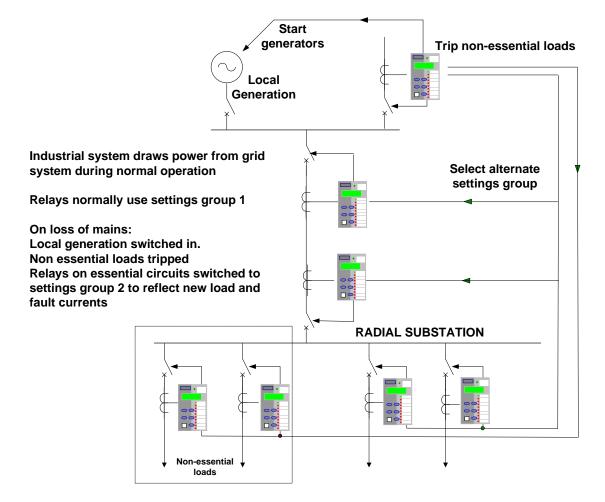

## 1.1 Multiple Settings Groups

Alternate settings groups can be used to reconfigure the relay during significant changes to system conditions e.g.

Primary plant switching in/out.

Summer/winter or day/night settings.

Switchable earthing connections.

Loss of Grid connection (see below)

Figure 1.0-1 Example Use of Alternative Settings Groups

## 1.2 Binary Inputs

Each Binary Input (BI) can be programmed to operate one or more of the relay functions, LEDs or output relays. These could be used to bring such digital signals as Inhibits for protection elements, the trip circuit supervision status, autoreclose control signals etc. into the Relay.

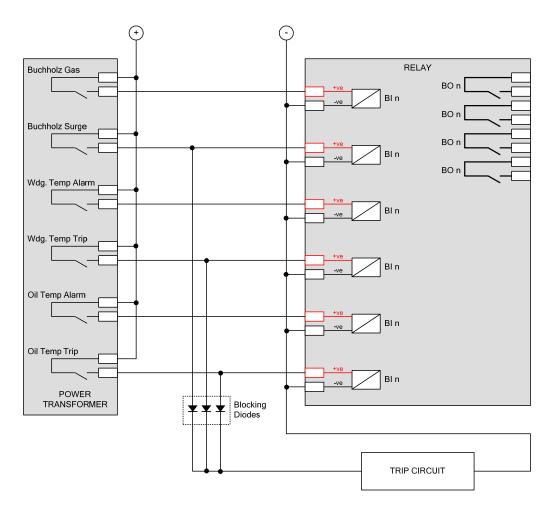

## 1.2.1 Alarm and Tripping Inputs

A common use of binary inputs is to provide indication of alarm or fault conditions e.g. transformer Buchholz Gas or Buchholz Surge conditions. The Binary Inputs are mapped to LED(s), waveform storage trigger and binary outputs. Note that transformer outputs which require high speed tripping, such as a Buchholz Surge, should be wired to a binary input to provide LED indication and also have a parallel connection wired to directly trip the circuit via a blocking diode, see figure. 1.2-1:

Figure 1.2-2 Example of Transformer Alarm and Trip Wiring

#### 1.2.2 The Effects of Capacitance Current

The binary inputs have a low minimum operate current and may be set for instantaneous operation. Consideration should be given to the likelihood of mal-operation due to capacitance current. Capacitance current can flow through the BI for example if an earth fault occurs on the dc circuits associated with the relay. The binary inputs will be less likely to mal-operate if they:

- 1 Have both the positive and negative switched (double-pole switched).

- 2 Do not have extensive external wiring associated with them e.g. if the wiring is confined to the relay room.

Where a binary input is both used to influence a control function (e.g. provide a tripping function) and it is considered to be susceptible to mal-operation the external circuitry can be modified to provide immunity to such disturbances, see figure 1.2-2.

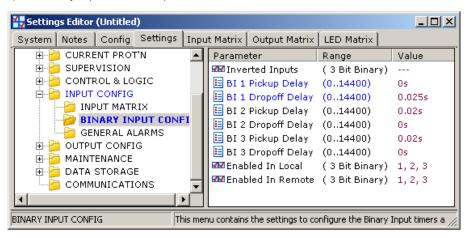

#### 1.2.3 AC Rejection

The default pick-up time delay of 20ms provides immunity to ac current for dc applications e.g. induced from cross site wiring.

Binary inputs can be configured for intentional operation from an ac power supply by setting pickup and drop-off timers for each binary input. 0ms PU and 25ms DO. If wiring to AC operate binary inputs is required to have a total length of more than 10 metres, screened twisted pair cable should be used.

If additional pickup or drop-off time delays are required by the scheme logic, this functionality can be achieved by programmable logic within the device.

Example.

An AC oprated Binary input is required to inhibit the 50-1 protection element with 100ms minimum pickup delay and 200ms minimum drop-off delay.

1) Set Binary Input 1 for AC operation:

2) Set quicklogic equation E1 to operate from Binary Input 1 and apply required delays:

System Notes Config Settings Input Matrix Output Matrix LED Matrix

Setting \ Output

BI 4 Operated

BI 5 Operated

BI 6 Operated

BI 7 Operated

BI 8 Operated

BI 8 Operated

BI 9 Operated

3) Set equation E1 to operate virtual I/O V1 in the Output Matrix:

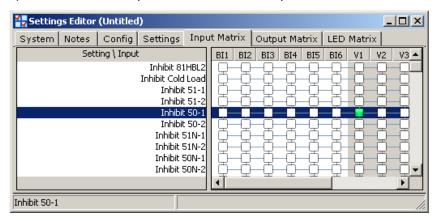

4) Set virtual I/O V1 to operate Inhibit 51-1 in the Input Matrix:

#### 1.2.4 Use of Binary Inputs in control and tripping circuits

Where a binary input is used to as part of a dc control function, for example tripping or closing a circuit breaker, it may be desirable to provide an enhanced level of immunity to prevent maloperation due to induced voltages.

This is most important where cross-site cabling is involved, as this is susceptible to induced voltages and will contribute to capacitive discharge currents under DC system earth fault conditions.

One method of enhancing the immunity of the binary input is to switch both positive and negative connections; however this is often not possible or desirable.

Where the battery voltage allows its use, the 88V binary input will give an added measure of immunity, compared to the 19V binary input, due to its higher minimum pickup voltage.

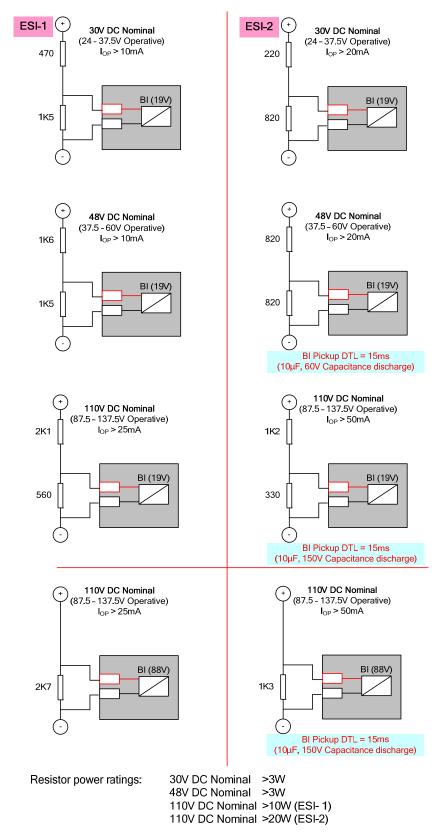

As a guide to suitable degrees of enhanced immunity, we have adopted the parameters laid down in U.K. standard EATS 48-4. This standard identifies two levels of immunity:

Category ESI 1 may be adopted for connections which do not include significant wiring runs or cabling outside the relay enclosure.

Category ESI 2 should be used for connections which include significant wiring runs or cabling outside the relay enclosure. This category also gives immunity to capacitive discharge currents.

The following diagrams show the external resistors which should be fitted to allow the binary input to comply with either of the above categories.

Fitting these components will raise the current required to operate the binary input, and hence makes it less susceptible to maloperation.

Where required, the minimum pickup delay for the binary input is stated on the diagram.

Resistors must be wired with crimped connections as they may run hot

Figure 1.2-3 Binary Input Configurations Providing Compliance with EATS 48-4 Classes ESI 1 and ESI 2

## 1.3 Binary Outputs

Binary Outputs are mapped to output functions by means of settings. These could be used to bring out such digital signals as trips, a general pick-up, plant control signals etc.

All Binary Outputs are Trip rated

Each can be defined as Self or Hand Reset. Self-reset contacts are applicable to most protection applications. Hand-reset contacts are used where the output must remain active until the user expressly clears it e.g. in a control scheme where the output must remain active until some external feature has correctly processed it.

Notes on Self Reset Outputs

With a failed breaker condition the relay may remain operated until current flow in the primary system is interrupted by an upstream device. The relay will then reset and attempt to interrupt trip coil current flowing through an output contact. Where this level is above the break rating of the output contact an auxiliary relay with heavy-duty contacts should be utilised.

#### **1.4 LEDs**

In the Output Configuration menu LEDs can be mapped to output functions by means of settings. These could be used to display such digital signals as trips, a general pick-up, plant control signals etc.

Each LED can be defined as Self or Hand Reset. Hand reset LEDs are used where the user is required to expressly acknowledge the change in status e.g. critical operations such as trips or system failures. Self-reset LEDs are used to display features which routinely change state, such as Circuit-Breaker open or close.

The status of hand reset LEDs is retained in capacitor-backed memory in the event of supply loss.

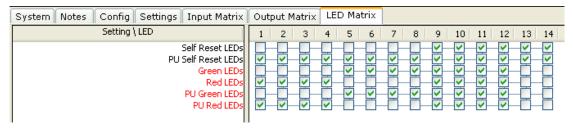

Each LED can be assigned as red, yellow or green in colour. There are two methods for doing this: -

In the LED Matrix tab, to assign the LED as a red colour select a box on the red row. To assign the LED as a green colour select a box on the green row. To assign the LED as a yellow colour, select boxes on both the red and green rows.

NB: If there are no boxes selected the LED will not illuminate.

Figure 1.4-1 LED configuration via the LED Matrix tab

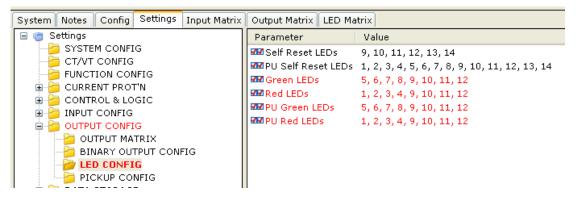

2) In the OUTPUT CONFIG\LED CONFIG menu in the Settings tab, to assign the required LED as a particular colour, either red or green, type the LED number in the appropriate row. To assign the required LED as a yellow colour, type the LED number in both red and green rows.

NB: If a LED number is not assigned that particular LED will not illuminate.

Figure 1.4-2 LED configuration via the Settings \ OUTPUT CONFIG \ LED CONFIG menu

## **Section 2: Protection Functions**

# 2.1 Time delayed overcurrent (51/51G/51N)

The 51-n characteristic element provides a number of time/current operate characteristics. The element can be defined as either an Inverse Definite Minimum Time Lag (IDMTL) or Definite Time Lag (DTL) characteristic. If an IDMTL characteristic is required, then IEC, ANSI/IEEE and a number of manufacturer specific curves are supported.

IDMTL characteristics are defined as "Inverse" because their tripping times are inversely proportional to the Fault Current being measured. This makes them particularly suitable to grading studies where it is important that only the Relay(s) closest to the fault operate. Discrimination can be achieved with minimised operating times.

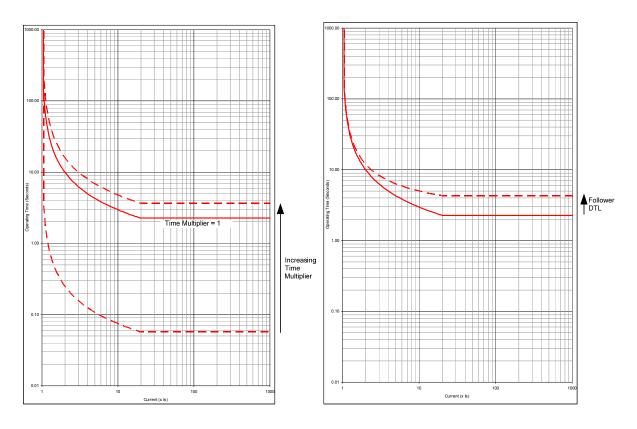

To optimise the grading capability of the relay additional time multiplier, 'Follower DTL' (Fig. 2.1-1) or 'Minimum Operate Time' (Fig. 2.1-2) settings can be applied.

Figure 2.1-1 IEC NI Curve with Time Multiplier and Follower DTL Applied

Figure 2.1-2 IEC NI Curve with Minimum Operate Time Setting Applied

To increase sensitivity, dedicated Earth fault elements are used. There should be little or no current flowing to earth in a healthy system so such relays can be given far lower pick-up levels than relays which detect excess current ( > load current) in each phase conductor. Such dedicated earth fault relays are important where the fault path to earth is a high-resistance one (such as in highly arid areas) or where the system uses high values of earthing resistor / reactance and the fault current detected in the phase conductors will be limited.

#### 2.1.1 Selection of Overcurrent Characteristics

Each pole has two independent over-current characteristics. Where required the two curves can be used:

To produce a composite curve

To provide a two stage tripping scheme

Where one curve is to be directionalised in the forward direction the other in the reverse direction.

The characteristic curve shape is selected to be the same type as the other relays on the same circuit or to grade with items of plant e.g. fuses or earthing resistors.

The application of IDMTL characteristic is summarised in the following table:

| OC/EF Curve Characteristic   | Application                                                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------------------------|

| IEC Normal Inverse (NI)      | Generally applied                                                                                                |

| ANSI Moderately Inverse (MI) |                                                                                                                  |

| IEC Very Inverse (VI)        | Used with high impedance paths where there is a significant difference between fault levels at protection points |

| ANSI Very Inverse (VI)       | between fault levels at protection points                                                                        |

| IEC Extreme Inversely (EI)   | Grading with Fuses                                                                                               |

| ANSI Extremely Inverse (EI)  |                                                                                                                  |

| IEC Long Time Inverse (LTI)  | Used to protect transformer earthing resistors having long withstand times                                       |

Table 2-1 Application of IDMTL Characteristics

#### 2.1.2 Reset Delay

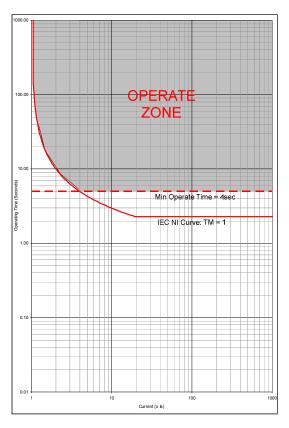

The increasing use of plastic insulated cables, both conventionally buried and aerial bundled conductors, have given rise to the number of flashing intermittent faults on distribution systems. At the fault position, the plastic melts and temporarily reseals the faulty cable for a short time after which the insulation fails again. The same phenomenon has occurred in compound-filled joint boxes or on 'clashing' overhead line conductors. The repeating occurrence of the fault can cause electromechanical disc relays to "ratchet" up and eventually trip the faulty circuit if the reset time of the relay is longer than the time between successive faults.

To mimic an electromechanical relay the relay can be user programmed for an IEC/ANSI DECAYING characteristic when an ANSI operate characteristic is applied. Alternatively a DTL reset (0 to 60 seconds) can be used with other operate characteristics.

For protection of cable feeders, it is recommended that a 60 second DTL reset be used.

On overhead line networks, particularly where reclosers are incorporated in the protected system, instantaneous resetting is desirable to ensure that, on multiple shot reclosing schemes, correct grading between the source relays and the relays associated with the reclosers is maintained.

Figure 2.1-3 Reset Delay

## 2.2 Voltage dependent overcurrent (51V)

Reduced voltage can indicate a fault on the system, it can be used to make the 51 elements more sensitive.

Typically Voltage Dependent Over-current (VDO) is applied to:

**Transformer Incomers**: Where the impedance of the transformer limits fault current the measured voltage level can be used to discriminate between load and fault current.

Long lines: Where the impedance of the line limits fault current the measured voltage level can be used to discriminate between load and fault current.

Generator circuits: When a Generator is subjected to a short circuit close to its terminals the short-circuit current follows a complex profile. After the initial "sub-transient" value, generally in the order of 7 to 10 times full load current, it falls rapidly (around 10 to 20ms) to the "transient" value. This is still about 5 to 7 times full load and would be sufficient to operate the protection's over-current elements. However the effect on armature reactance of the highly inductive short-circuit current is to increase significantly the internal impedance to the synchronous reactance value. If the Automatic Voltage Regulation (AVR) system does not respond to increase the excitation, the fault current will decay over the next few seconds to a value below the full load current. This is termed the steady state fault current, determined by the Generator's synchronous reactance (and pre-fault excitation). It will be insufficient to operate the protection's over-current elements and the fault will not be detected. Even if AVR is active, problems may still be encountered. The AVR will have a declared minimum sustained fault current and this must be above the protection over-current settings. Close-in short circuit faults may also cause the AVR to reach its safety limits for supplying maximum excitation boost, in the order of several seconds, and this will result in AVR internal protection devices such as diode fuses to start operating. The generator excitation will then collapse, and the situation will be the same as when no AVR was present. The fault may again not be detected.

Current grading remains important since a significant voltage reduction may be seen for faults on other parts of the system. An inverse time operating characteristic must therefore be used.

The VDO Level - the voltage setting below which the more sensitive operating curve applies - must be set low enough to discriminate between short-circuits and temporary voltage dips due to overloads. However, it must also be high enough to cover a range of voltage drops for different circuit configurations, from around 0.6Vn to almost zero. Typically it will be set in the range 0.6 to 0.8Vn.

# 2.3 Cold Load Settings (51c)

Once a Circuit-Breaker has been open for a period of time, higher than normal levels of load current may flow following CB re-closure e.g. heating or refrigeration plant. The size and duration of this current is dependent upon the type of load and the time that the CB is open.

The feature allows the relay to use alternative Shaped Overcurrent (51c) settings when a Cold Load condition is identified. The cold load current and time multiplier settings will normally be set higher than those of the normal overcurrent settings.

The relay will revert to its usual settings (51-n) after elapse of the cold load period. This is determined either by a user set delay, or by the current in all 3-phases falling below a set level (usually related to normal load levels) for a user set period.

## 2.4 Instantaneous Overcurrent (50/50G/50N)

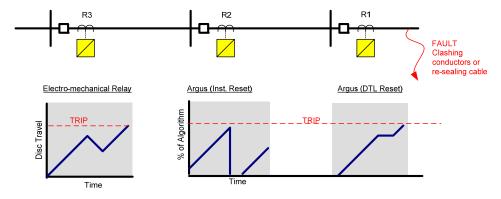

Each instantaneous element has an independent setting for pick-up current and a follower definite time lag (DTL) which can be used to provide time grading margins, sequence co-ordination grading or scheme logic. The "instantaneous" description relates to the pick-up of the element rather than its operation.

Figure 2.4-4 General Form of DTL Operate Characteristic

Instantaneous elements can be used in current graded schemes where there is a significant difference between the fault current levels at different relay point. The Instantaneous element is set to pick up at a current level above the maximum Fault Current level at the next downstream relay location, and below its own minimum fault current level. The protection is set to operate instantaneously and is often termed 'Highset Overcurrent'. A typical application is the protection of transformer HV connections – the impedance of the transformer ensuring that the LV side has a much lower level of fault current.

The 50-n elements have a very low transient overreach i.e. their accuracy is not appreciably affected by the initial dc offset transient associated with fault inception.

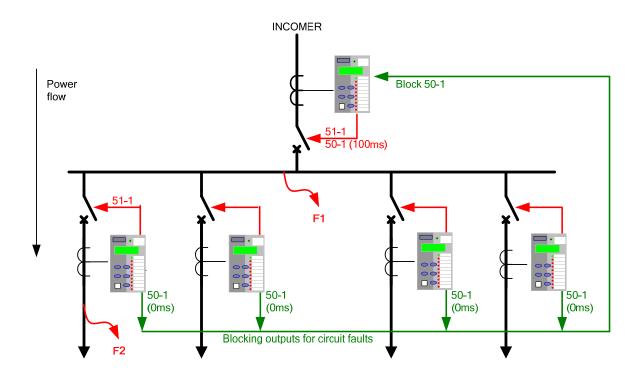

#### 2.4.1 Blocked Overcurrent Protection Schemes

A combination of instantaneous and DTL elements can be used in blocked overcurrent protection schemes. These protection schemes are applied to protect substation busbars or interconnectors etc. Blocked overcurrent protection provides improved fault clearance times when compared against normally graded overcurrent relays.

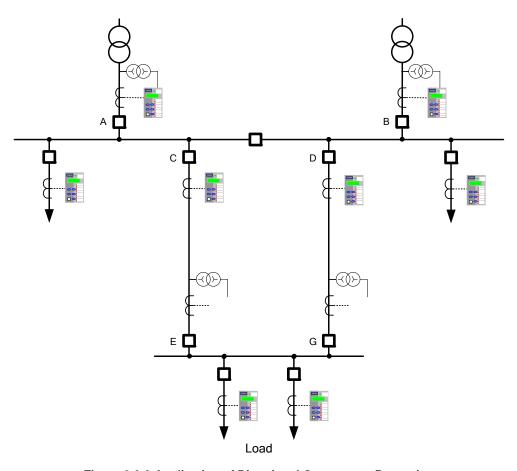

The blocked overcurrent scheme of busbar protection shown in Figure 2.4-2 illustrates that circuit overcurrent and earth fault protection relays can additionally be configured with busbar protection logic.

The diagram shows a substation. The relay on the incomer is to trip for busbar faults (F1) but remain inoperative for circuit faults (F2).

In this example the overcurrent and earth fault settings for the incomer 50-1 element are set to below the relevant busbar fault levels. 50-1 time delay is set longer than it would take to acknowledge receipt of a blocking signal from an outgoing circuit.

Close up faults on the outgoing circuits will have a similar fault level to busbar faults. As the incomer 50-1 elements would operate for these faults it is necessary to provide a blocking output from the circuit protections. The 50-1 elements of the output relays are given lower current settings than the incomer 50-1 settings, the time delay is set to 0ms. The output is mapped to a contact. The outgoing relay blocking contacts of all circuits are wired in parallel and this wiring is also connected to a BI on the incomer relay. The BI on the incomer relay is mapped to block its 50-1 element.

Figure 2.4-5 Blocking Scheme Using Instantaneous Overcurrent Elements

Typically a time delay as low as 50ms on the incomer 50-1 element will ensure that the incomer is not tripped for outgoing circuit faults. However, to include for both equipment tolerances and a safety margin a minimum time delay of 100ms is recommended.

This type of scheme is very cost effective and provides a compromise between back-up overcurrent busbar protection and dedicated schemes of busbar protection.

Instantaneous elements are also commonly applied to autoreclose schemes to grade with downstream circuit reclosers and maximise the probability of a successful auto-reclose sequence – see section 4.

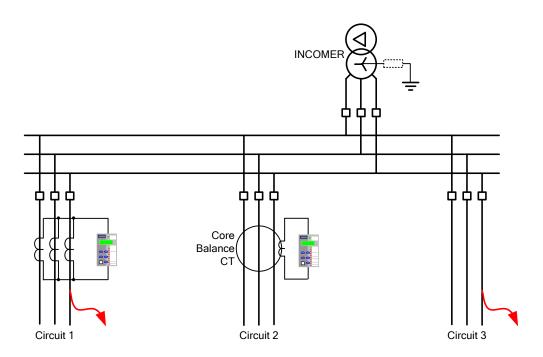

## 2.5 Sensitive Earth-fault Protection (50SEF)

Earth fault protection is based on the assumption that fault current levels will be limited only by the earth fault impedance of the line and associated plant. However, it may be difficult to make an effective short circuit to earth due to the nature of the terrain e.g. dry earth, desert or mountains. The resulting earth fault current may therefore be limited to very low levels.

Sensitive earth fault (SEF) protection is used to detect such faults. The relays have a low burden, so avoiding unacceptable loading of the CTs at low current settings. Only the fundamental component is used to avoid pick up from harmonics.

SEF provides a backup to the main protection. A DTL characteristic with a time delay of several seconds is typically applied ensuring no interference with other discriminative protections. A relatively long time delay can be tolerated since fault current is low and it is impractical to grade SEF protection with other earth fault protections. Although not suitable for grading with other forms of protection SEF relays may be graded with each other.

Where very sensitive current settings are required then it is preferable to use a core balance CT rather than wire into the residual connection of the line CTs. The turns ratio of a core balance CT can be much smaller than that of phase conductors as they are not related to the rated current of the protected circuit. Since only one core is used, the CT magnetising current losses are also reduced by a factor of 3.

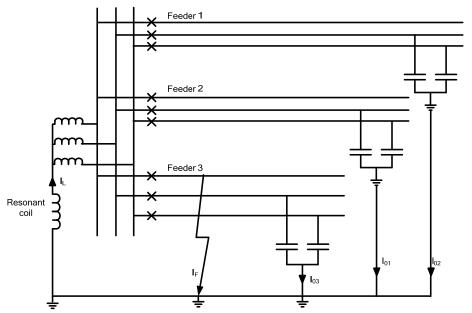

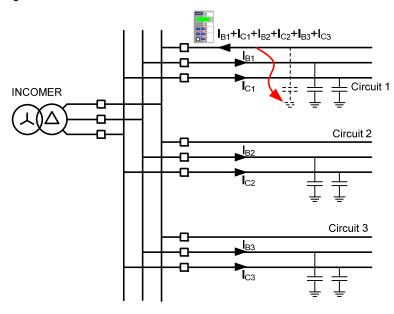

Figure 2.5-6 Sensitive Earth Fault Protection Application

There are limits to how sensitive an SEF relay may be set since the setting must be above any line charging current levels that can be detected by the relay. On occurrence of an out of zone earth fault e.g. on circuit 3 the elevation of sound phase voltage to earth in a non-effectively earthed system can result in a zero sequence current of up 3 times phase charging current flowing through the relay location.

The step change from balanced 3-phase charging currents to this level of zero sequence current includes transients. It is recommended to allow for a transient factor of 2 to 3 when determining the limit of charging current. Based on the above considerations the minimum setting of a relay in a resistance earthed power system is 6 to 9 times the charging current per phase.

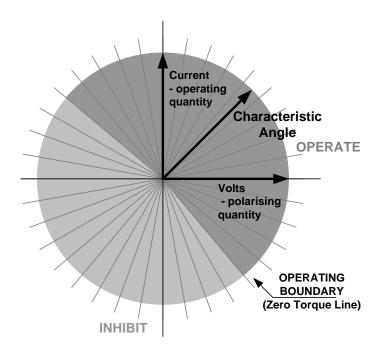

# 2.6 Directional Protection (67)

Each overcurrent stage can operate for faults in either forward or reverse direction. Convention dictates that forward direction refers to power flow away from the busbar, while reverse direction refers to power flowing towards the busbar.

The directional phase fault elements, 67/50 and 67/51, work with a Quadrature Connection to prevent loss of polarising quantity for close-in phase faults. That is, each of the current elements is directionalised by a voltage derived from the other two phases.

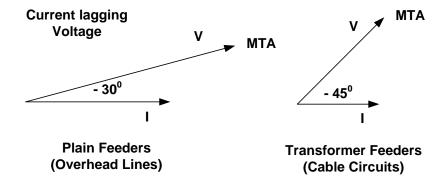

This connection introduces a 90° Phase Shift (Current leading Voltage) between reference and operate quantities which must be allowed for in the Characteristic Angle setting. This is the expected fault angle, sometimes termed the Maximum Torque Angle (MTA) as an analogy to older Electro-mechanical type relays

Example: Expected fault angle is -30° (Current lagging Voltage) so set Directional Angle to: +90° -30° = +60°.

A fault is determined to be in the selected direction if its phase relationship lies within a quadrant +/- 85° either side of the Characteristic Angle setting.

Figure 2.6-7 Directional Characteristics

A number of studies have been made to determine the optimum MTA settings e.g. W.K Sonnemann's paper "A Study of Directional Element Connections for Phase Relays". Figure 2.6-1 shows the most likely fault angle for phase faults on Overhead Line and Cable circuits.

Figure 2.6-8 Phase Fault Angles

Directional overcurrent elements allow greater fault selectivity than non-directional elements for interconnected systems where fault current can flow in both directions through the relaying point. Consider the network shown in fig. 2.6-3.

The Circuit breakers at A, B, E and G have directional overcurrent relays fitted since fault current can flow in both directions at these points. The forward direction is defined as being away from the busbar and against the direction of normal load current flow. These forward looking IDMTL elements can have sensitive settings applied i.e. low current and time multiplier settings. Note that 7SR12 relays may be programmed with forward, reverse and non-directional elements simultaneously when required by the protection scheme.

Figure 2.6-9 Application of Directional Overcurrent Protection

Figure 2.6-4 Feeder Fault on Interconnected Network

Considering the D-G feeder fault shown in fig. 2.6-4: the current magnitude through breakers C and D will be similar and their associated relays will have similar prospective operate times. To ensure that only the faulted feeder is isolated G FWD must be set to be faster than C. Relay G will thus Trip first on FWD settings, leaving D to operate to clear the fault. The un-faulted Feeder C-E maintains power to the load.

Relays on circuits C and D at the main substation need not be directional to provide the above protection scheme. However additional directional elements could be mapped to facilitate a blocked overcurrent scheme of busbar protection.

At A and B, forward looking directional elements enable sensitive settings to be applied to detect transformer faults whilst reverse elements can be used to provide back-up protection for the relays at C and D.

By using different settings for forward and reverse directions, closed ring circuits can be set to grade correctly whether fault current flows in a clockwise or counter clockwise direction i.e. it may be practical to use only one relay to provide dual directional protection.

#### 2.6.1 2 Out of 3 Logic

Sensitive settings can be used with directional overcurrent relays since they are directionalised in a way which opposes the flow of normal load current i.e. on the substation incomers as shown on fig. 2.6-4. However on occurrence of transformer HV or feeder incomer phase-phase faults an unbalanced load current may still flow as an unbalanced driving voltage is present. This unbalanced load current during a fault may be significant where sensitive overcurrent settings are applied - the load current in one phase may be in the operate direction and above the relay setting.

Where this current distribution may occur then the relay is set to CURRENT PROTECTION>PHASE OVERCURRENT> 67 2-out-of-3 Logic = ENABLED

Enabling 2-out-of-3 logic will prevent operation of the directional phase fault protection for a single phase to earth fault. Dedicated earth-fault protection should therefore be used if required.

## 2.7 Directional Earth-Fault (50/51G, 50/51N, 50/51SEF)

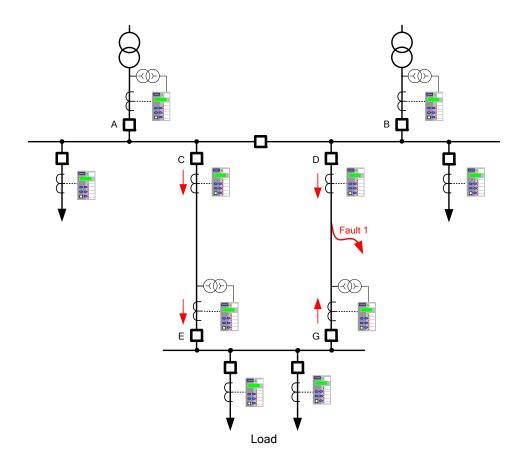

The directional earth-fault elements, either measured directly or derived from the three line currents the zero sequence current (operate quantity) and compare this against the derived zero phase sequence voltage (polarising quantity). Chapter 1 of the Technical Manual 'Description of Operation' details the method of measurement. The required setting is entered directly as dictated by the system impedances.

Example: Expected fault angle is -45° (i.e. residual current lagging residual voltage) therefore **67G Char Angle** = **-45**°

However directional earth elements can be selectable to use either ZPS or NPS Polarising. This is to allow for the situation where ZPS voltage is not available; perhaps because a 3-limb VT is being used. Care must be taken as the Characteristic Angle will change if NPS Polarising is used.

Once again the fault angle is completely predictable, though this is a little more complicated as the method of earthing must be considered.

Figure 2.7-1 Earth Fault Angles

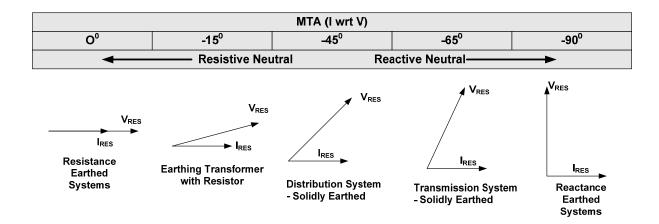

#### 2.7.1 Compensated Coil Earthing Networks

In compensated networks the Resonant Coil (Petersen coil) is tuned to match the capacitive charging currents such that when an earth fault occurs, negligible fault current will flow. However, resistive losses in the primary conductors and also in the earthing coil will lead to resistive (wattmetric) components which can be measured by the 50/51SEF elements and used to indicate fault position. Core balance CTs are recommended for this application to achieve the necessary accuracy of residual current measurement.

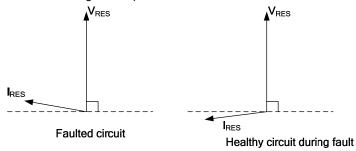

Figure 2.7-1 Earth fault current distribution in Compensated network

Three methods are commonly employed to detect the wattmetric current. The 7SR12 relay has customer settings that can be configured to provide each of these methods.

Figure 2.7-2 Earth fault current direction in compensated network

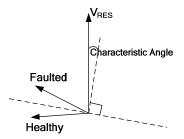

(i) The directional boundary can be used to discriminate between healthy and faulted feeders. The characteristic angle is set to approximately 0° and the boundary at +90° used to detect the direction of the resistive component within the residual current. Setting of the boundary is critical to discriminate between faulted and unfaulted circuits. Setting '67SEF Compensated Network' to 'Enabled' will set the directional boundaries to ±87° around the characteristic angle, fine adjustment of the boundary may be necessary using the characteristic angle setting.

Figure 2.7-3 Adjustment of Characteristic Angle

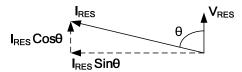

(ii) The element measuring circuit can be subjected to only the cosine component of residual current i.e. to directly measure the real (wattmetric) current due to losses. The current  $I_{RES}Cos(\theta-\emptyset)$  is calculated where  $\theta$  is the measured phase angle between residual current and voltage and  $\emptyset$  is the characteristic angle. This option is selected by setting 'Ires Select' to 'Ires Real'. The characteristic angle should be set to  $0^{\circ}$ .

Figure 2.7-4 Cosine component of current

(iii) Application of a Wattmetric power characteristic. The directional 50/51 SEF element operation is subject to an additional sensitive residual power element which operates only on the real (wattmetric) component of residual power.

## 2.7.2 Isolated Networks

During earth faults on isolated distribution networks there is no fault current path and subsequently no fault current will flow. However, the phase-neutral capacitive charging current of the healthy phases for the whole connected network will be supplied through the fault path. This will produce a current at the relay which can be used to detect the presence of the fault. It appears as a residual current which lags the residual voltage by 90°. The characteristic angle should be set to -90°.

Figure 2.7-5 Earth fault current in isolated network

Some customers prefer to use only the sine (reactive) component of the residual current which can be easily achieved by setting 'Ires Select' to 'Ires Real' to select the operating current to  $I_{RES}Cos(\theta-\emptyset)$  and setting the characteristic angle  $\emptyset$  to -90°.

#### 2.7.3 Minimum Polarising Voltage

The correct residual voltage direction must be measured to allow a forward/reverse decision to be made. Minimum polarising voltage setting can be used to prevent tripping when fault conditions are such that significant residual voltage is not generated and the directional decision would be unreliable. The setting must allow for error in voltage measurement due to VT inaccuracy and connection. It can be used to improve stability under non-fault conditions during unbalanced load, when earth fault elements with very sensitive current settings are applied. This is ensured by selecting a setting which is near to the minimum expected residual voltage during fault conditions.

High impedance earthing methods, including compensated and isolated systems, will result in high levels of residual voltage, up to 3 times normal phase to neutral voltage, during earth faults. The minimum polarising voltage can therefore be increased to allow very low residual current settings to be applied without risk of operation during unbalanced load conditions.

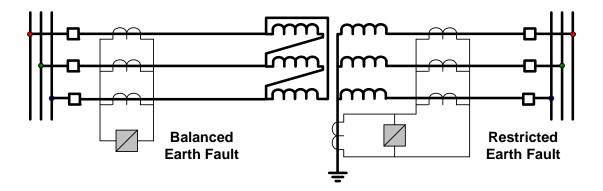

## 2.8 High Impedance Restricted Earth Fault Protection (64H)

Restricted Earth Fault (REF) protection is applied to Transformers to detect low level earth faults in the transformer windings. Current transformers are located on all connections to the transformer. During normal operation or external fault conditions no current will flow in the relay element. When an internal earth fault occurs, the currents in the CTs will not balance and the resulting unbalance flows through the relay.

The current transformers may saturate when carrying high levels of fault current. The high impedance name is derived from the fact that a resistor is added to the relay leg to prevent relay operation due to CT saturation under through fault conditions.

The REF Trip output is configured to provide an instantaneous trip output from the relay to minimise damage from developing winding faults.

The application of the element to a delta-star transformer is shown in Figure 2.8-1. Although the connection on the relay winding is more correctly termed a Balanced Earth-Fault element, it is still usually referred to as Restricted Earth Fault because of the presence of the transformer.

Figure 2.8-1 Balanced and Restricted Earth-fault protection of Transformers

The calculation of the value of the Stability Resistor is based on the worst case where one CT fully saturates and the other balancing CT does not saturate at all. A separate Siemens Protection Devices Limited Publication is available covering the calculation procedure for REF protection. To summarise this:

The relay Stability (operating) Vs voltage is calculated using worst case lead burden to avoid relay operation for through-fault conditions where one of the CTs may be fully saturated. The required fault setting (primary operate current) of the protection is chosen; typically, this is between 10 % and 25 % of the protected winding rated current. The relay setting current is calculated based on the secondary value of the operate current, note, however, that the summated CT magnetising current @ Vs must be subtracted to obtain the required relay operate current setting.

Since the relay operate current setting and stability/operating voltage are now known, a value for the series resistance can now be calculated.

A check is made as to whether a Non-Linear Resistor is required to limit scheme voltage during internal fault conditions – typically where the calculated voltage is in excess of 2kV.

The required thermal ratings for external circuit components are calculated.

overcurrent elements

series stabilising resistor 25 REF element

Composite overcurrent and REF protection can be provided using a multi-element relay as shown below.

Figure 2.8-2 Composite Overcurrent and Restricted Earth-fault Protection

non-linear resistor

Although core-balance CTs are traditionally used with elements requiring sensitive pickup settings, cost and size usually precludes this on REF schemes. Instead single-Phase CTs are used and their secondary's connected in parallel.

Where sensitive settings are required, the setting must be above any line charging current levels that can be detected by the relay.

On occurrence of an out of zone earth fault the elevation of sound phase voltage to earth in a non-effectively earthed system can result in a zero sequence current of up 3 times phase charging current flowing through the relay location.

The step change from balanced 3-phase charging currents to this level of zero sequence current includes transients. It is recommended to allow for a transient factor of 2 to 3 when determining the limit of charging current. Based on the above considerations the minimum setting of a relay in a resistance earthed power system is 6 to 9 times the charging current per phase.

High impedance differential protection is suitable for application to auto transformers as line currents are in phase and the secondary current through the relay is balanced to zero by the use of CTs ratios at all three terminals. High impedance protection of this type is very sensitive and fast operating for internal faults.

# 2.9 Negative Phase Sequence Overcurrent (46NPS)

The presence of Negative Phase Sequence (NPS) current indicates an unbalance in the phase currents, either due to a fault or unbalanced load.

NPS current presents a major problem for 3-phase rotating plant. It produces a reaction magnetic field which rotates in the opposite direction, and at twice the frequency, to the main field created by the DC excitation system. This induces double-frequency currents into the rotor which cause very large eddy currents in the rotor body. The resulting heating of the rotor can be severe and is proportional to  $(I_2)^2$  t.

Generators and Motors are designed, manufactured and tested to be capable of withstanding unbalanced current for specified limits. Their withstand is specified in two parts; continuous capability based on a figure of  $I_2$ , and short time capability based on a constant, K, where  $K = (I_2)^2$  t. NPS overcurrent protection is therefore configured to match these two plant characteristics.

## 2.10 Undercurrent (37)

Undercurrent elements are used in control logic schemes such as Auto-Changeover Schemes, Auto-Switching Interlock and Loss of Load. They are used to indicate that current has ceased to flow or that a low load situation exists. For this reason simple Definite Time Lag (DTL) elements may be used.

For example, once it has been determined that fault current has been broken – the CB is open and no current flows – an auto-isolation sequence may safely be initiated.

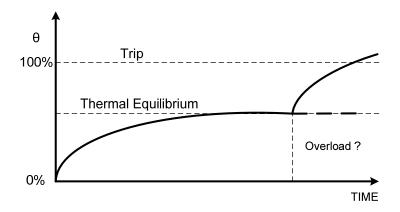

# 2.11 Thermal Overload (49)

The element uses measured 3-phase current to estimate the real-time Thermal State,  $\theta$ , of cables or transformers. The Thermal State is based on both past and present current levels.

$\theta$  = 0% for unheated equipment, and  $\theta$  = 100% for maximum thermal withstand of equipment or the Trip threshold.

Figure 2.11-3 Thermal Overload Heating and Cooling Characteristic

For given current level, the Thermal State will ramp up over time until Thermal Equilibrium is reached when Heating Effects of Current = Thermal Losses.

The heating / cooling curve is primarily dependant upon the Thermal Time Constant. This must be matched against that quoted for the item of plant being protected. Similarly the current tripping threshold,  $I_{\theta}$ , is related to the thermal withstand of the plant.

Thermal Overload is a slow acting protection, detecting faults or system conditions too small to pick-up fast acting protections such as Phase Overcurrent. An Alarm is provided for  $\theta$  at or above a set % of capacity to indicate that a potential trip condition exists and that the system should be scrutinised for abnormalities.

# 2.12 Under/Over Voltage Protection (27/59)

Power system under-voltages on may occur due to:

System faults.

An increase in system loading,

Non-energized power system e.g. loss of an incoming transformer

During normal system operating conditions regulating equipment such as transformer On Load Tap Changers (OLTC) and generator Automatic Voltage Regulators (AVR) ensure that the system runs within acceptable voltage limits.

Undervoltage/DTL elements can be used to detect abnormal undervoltage conditions due to system overloads. Binary outputs can be used to trip non-essential loads - returning the system back to its normal operating levels. This 'load shedding' should be initiated via time delay elements so avoiding operation during transient disturbances. An undervoltage scheme (or a combined under frequency/under voltage scheme) can provide faster tripping of non-essential loads than under-frequency load shedding so minimising the possibility of system instability.

Where a transformer is supplying 3-phase motors a significant voltage drop e.g. to below 80% may cause the motors to stall. An undervoltage element can be set to trip motor circuits when the voltage falls below a preset value so that on restoration of supply an overload is not caused by the simultaneous starting of all the motors. A time delay is required to ensure voltage dips due to remote system faults do not result in an unnecessary disconnection of motors.

To confirm presence/loss of supply, the voltage elements should be set to values safely above/below that where a normal system voltage excursion can be expected. The switchgear/plant design should be considered. The 'Dead' level may be very near to the 'live' level or may be significantly below it. The variable hysteresis setting allows the relay to be used with all types of switchgear.

System over-voltages can damage component insulation. Excessive voltage may occur for:

Sudden loss of load

A tap changer run-away condition occurs in the high voltage direction,

Generator AVR equipment malfunctions or

Reactive compensation control malfunctions.

System regulating equipment such as transformer tap changers and generator AVRs may correct the overvoltage – unless this equipment mal-functions. The overvoltage/DTL elements can be used to protect against damage caused by system overvoltages.

If the overvoltage condition is small a relatively long DTL time delay can be used. If the overvoltage is more severe then another element, set at a higher pickup level and with a shorter DTL can be used to isolate the circuit more quickly. Alternatively, elements can be set to provide alarm and tripping stages, with the alarm levels set lower than the tripping stages.

The use of DTL settings allows a grading system to be applied to co-ordinate the network design, the regulating plant design, system plant insulation withstand and with other overvoltage relays elsewhere on the system. The DTL also prevents operation during transient disturbances.

The use of IDMTL protection is not recommended because of the difficulty of choosing settings to ensure correct co-ordination and security of supply.

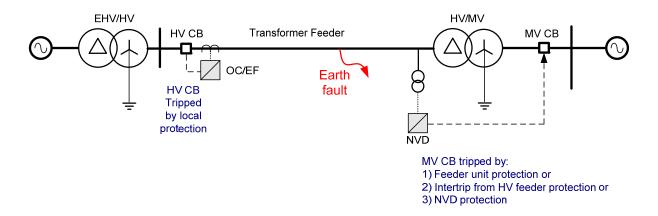

## 2.13 Neutral Overvoltage (59N)

Neutral Voltage Displacement (NVD) protection is used to detect an earth fault where little or no earth current flows

This can occur where a feeder has been tripped at its HV side for an earth fault, but the circuit is still energised from the LV side via an unearthed transformer winding. Insufficient earth current would be present to cause a trip, but residual voltage would increase significantly; reaching up to 3-times the normal phase-earth voltage level.

If Neutral Overvoltage protection is used, it must be suitably time graded with other protections in order to prevent unwanted tripping for external system earth faults.

Figure 2.13-4 NVD Application

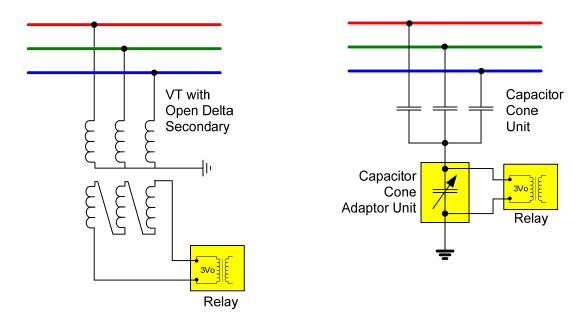

Typically NVD protection measures the residual voltage  $(3V_0)$  directly from an open delta VT or from capacitor cones – see fig. 2.13-2 below.

Figure 2.13-5 NVD Protection Connections

#### 2.13.1 Application with Capacitor Cone Units

Capacitor cones provide a cost effective method of deriving residual voltage. The wide range of capacitor cone component values used by different manufacturers means that the relay cannot be connected directly to the cones.

The external adaptor unit contains parallel switched capacitors that enable a wide range of values to be selected using a DIL switch and hence the Capacitor Cone output can be scaled to the standard relay input range.

## 2.13.2 Derived NVD Voltage

Alternatively NVD voltage can be derived from the three phase to neutral voltages, this setting is available within the relay. Note with this method the NVD protection may mal-operate during a VT Fail condition.

## 2.14 Negative Phase Sequence Overvoltage (47)

Negative Phase Sequence (NPS) protection detects phase unbalances and is widely used in protecting rotating plant such as motors and generators. However such protection is almost universally based on detecting NPS Current rather than Voltage. This is because the NPS impedance of motors etc. is much less than the Positive Phase Sequence (PPS) impedance and therefore the ratio of NPS to PPS Current is much higher than the equivalent ratio of NPS to PPS Voltage.

NPS Voltage is instead used for monitoring busbar supply quality rather than detecting system faults. The presence of NPS Voltage is due to unbalanced load on a system. Any system voltage abnormality is important since it will affect every motor connected to the source of supply and can result in mass failures in an industrial plant.

The two NPS Voltage DTL elements should therefore be used as Alarms to indicate that the level of NPS has reached abnormal levels. Remedial action can then be taken, such as introducing a Balancer network of capacitors and inductors. Very high levels of NPS Voltage indicate incorrect phase sequence due to an incorrect connection.

# 2.15 Under/Over Frequency (81)

During normal system operation the frequency will continuously vary over a relatively small range due to the changing generation/load balance. Excessive frequency variation may occur for:

Loss of generating capacity, or loss of mains supply (underfrequency): If the governors and other regulating equipment cannot respond to correct the balance, a sustained underfrequency condition may lead to a system collapse.

Loss of load – excess generation (overfrequency): The generator speeds will increase causing a proportional frequency rise. This may be unacceptable to industrial loads, for example, where the running speeds of synchronous motors will be affected.

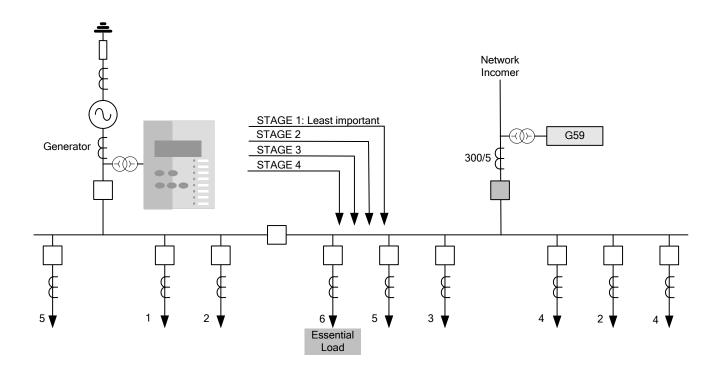

In the situation where the system frequency is falling rapidly it is common practise to disconnect non-essential loads until the generation-load balance can be restored. Usually, automatic load shedding, based on underfrequency is implemented. Underfrequency relays are usually installed on the transformer incomers of distribution or industrial substations as this provides a convenient position from which to monitor the busbar frequency. Loads are disconnected from the busbar (shed) in stages until the frequency stabilises and returns to an acceptable level.

The relay has four under/over frequency elements.

An example scheme may have the first load shedding stage set just below the nominal frequency, e.g. between 49.0 - 49.5Hz. A time delay element would be associated with this to allow for transient dips in frequency and to provide a time for the system regulating equipment to respond. If the first load shedding stage disconnects sufficient plant the frequency will stabilise and perhaps return to nominal. If, however, this is not sufficient then a second load shedding stage, set at a lower frequency, will shed further loads until the overload is relieved. This process will continue until all stages have operated. In the event of the load shedding being unsuccessful, a final stage of underfrequency protection should be provided to totally isolate all loads before plant is damaged, e.g. due to overfluxing.

An alternative type of load shedding scheme would be to set all underfrequency stages to about the same frequency setting but to have different length time delays set on each stage. If after the first stage is shed the frequency doesn't recover then subsequent stages will shed after longer time delays have elapsed.

Figure 2.15-1 Load Shedding Scheme Using Under-Frequency Elements

## **Section 3: CT Requirements**

# 3.1 CT Requirements for Overcurrent and Earth Fault Protection

#### 3.1.1 Overcurrent Protection CTs

- a) For industrial systems with relatively low fault current and no onerous grading requirements a class 10P10 with VA rating to match the load.

- b) For utility distribution networks with relatively high fault current and several grading stages a class 5P20, with VA rating to match the load.

Note: if an accuracy limit factor is chosen which is much lower than the maximum fault current it will be necessary to consider any effect on the protection system performance and accuracy e.g. grading margins.

For idmtl applications, because the operating time at high fault current is a definite minimum value, partial saturation of the CT at values beyond the overcurrent factor has only a minimal effect. However, this must be taken into account in establishing the appropriate setting to ensure proper grading.

c) For dtl applications utilities as for (b) above - a class 5P10 (or 20), with rated burden to suit the load.

Note: Overcurrent factors do not need to be high for definite time protection because once the setting is exceeded magnitude accuracy is not important. Often, however, there is also the need to consider instantaneous HighSet overcurrent protection as part of the same protection system and the settings would normally be of the order of 10x the CT rating or higher. Where higher settings are to be used then the overcurrent factor must be raised accordingly, e.g. to P20.

#### 3.1.2 Earth Fault Protection CTs

Considerations and requirements for earth fault protection are the same as for Phase fault. Usually the relay employs the same CT's e.g. three phase CTs star connected to derive the residual earth fault current.

The accuracy class and overcurrent accuracy limit factors are therefore already determined and for both these factors the earth fault protection requirements are normally less onerous than for overcurrent.

# 3.2 CT Requirements for High Impedance Restricted Earth Fault Protection

For high impedance REF it is recommended that:

Low reactance CTs to IEC Class PX are used, this allows a sensitive current setting to be applied.

All CT's should, if possible have identical turns ratios.

The knee point voltage of the CTs must be greater than 2 x 64H setting voltage Vs.

Where the REF function is used then this dictates that the other protection functions are also used with class PX CTs

A full explanation of how to specify CTs for use with REF protection, and set REF relays is available on our website: www.siemens.com/energy.

## **Section 4: Control Functions**

## 4.1 Auto-reclose Applications

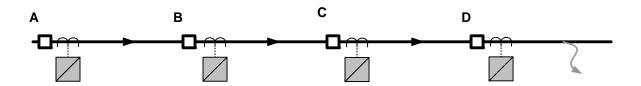

Automatic circuit reclosing is extensively applied to overhead line circuits where a high percentage of faults

that occur are of a transient nature. By automatically reclosing the circuit-breaker the feature attempts to

minimise the loss of supply to the customer and reduce the need for manual intervention.

The function supports up to 4 ARC sequences. That is, 4 x Trip / Recloses followed by a Trip & Lockout. A lockout condition prevents any further automatic attempts to close the circuit-breaker. The number of sequences selected depends upon the type of faults expected. If there are a sufficient percentage of semi-permanent faults which could be burnt away, e.g. fallen branches, a multi shot scheme would be appropriate. Alternatively, if there is a high likelihood of permanent faults, a single shot scheme would minimise the chances of causing damage by reclosing onto a fault. In general, 80% of faults will be cleared by a single Trip and Reclose sequence. A further 10% will be cleared by a second Trip and Reclose. Different sequences can be selected for different fault types (Phase/Earth/Sensitive Earth faults).

The Deadtime is the interval between the trip and the CB close pulse being issued. This is to allow for the line to go 'dead' after the fault is cleared. The delay chosen is a compromise between the need to return the line to service as soon as possible and prevented unnecessary trips through re-closing too soon. The Reclaim Time is the delay following a re-closure before the line can be considered back in service. This should be set long enough to allow for protection operation for the same fault, but not so long that two separate faults could occur in the same Autoreclose (ARC) sequence and cause unnecessary lockouts.

The Sequence Fail Timer provides an overall maximum time limit on the ARC operation. It should therefore be longer than all the set delays in a complete cycle of ARC sequences; trip delays, Deadtimes, Reclaim Time etc. Generally this will only be exceeded if the circuit-breaker has either failed to open or close.

Since large fault currents could potentially damage the system during a prolonged ARC sequence, there are also settings to identify which protection elements are High-sets and these can cause an early termination of the sequence.

Where a relay is to operate as part of an ARC scheme involving a number of other relays, the feature attempts to clear any faults quickly without regard to normal fault current grading. It does this by setting each Trip element to be either Delayed or Instantaneous. Instantaneous Trips are set to operate at just above maximum load current with small delays while Delayed Trips are set to suit actual fault levels and with delays suitable for current grading.

A typical sequence would be 2 Instantaneous Trips followed by a Delayed Trip & Lockout:

- When any fault occurs, the relay will trip instantaneously and then reclose.

- If this does not clear the fault, the relay will do the same again.

- If this still does not clear the fault, the fault is presumed to be permanent and the next Trip will be Delayed and so suitable for grading with the rest of the network. Thus allowing downstream protection time to operate.

- The next trip will Lockout the ARC sequence and prevent further recloses.

It is important that all the relays in an ARC scheme shadow this process – advancing through their own ARC sequences when a fault is detected by an element pickup even though they are not actually causing a trip or reclose. This is termed Sequence Co-ordination and prevents an excessive number of recloses as each successive relay attempts to clear the fault in isolation. For this reason each relay in an ARC scheme must be set with identical Instantaneous and Delayed sequence of trips.

Figure 4.1-1 Sequence Co-ordination

The relay closest to the fault (D) would step through its Instantaneous Trips in an attempt to clear the fault. If unsuccessful, the relay would move to a Delayed Trip sequence.

The other relays in the network (A, B and C) would recognise the sequence of Pick-up followed by current switch-off as ARC sequences. They would therefore also step to their Delayed Trip to retain co-ordination with the respective downstream devices.

The next Trip would be subject to current grading and Lockout the ARC sequence such that the fault is cleared by the correct CB.

## 4.1.1 Auto-Reclose Example 1

Requirement: Settings shall provide four phase fault recloses – two instantaneous and two delayed - and only two delayed recloses for faults detected by the SEF protection.

Proposed settings include:

CONTROL & LOGIC > AUTORECLOSE PROT'N:

79 P/F Inst Trips: 50-1

79 P/F Delayed Trips: 51-1

79 SEF Delayed Trips: 51SEF-1

CONTROL & LOGIC > AUTORECLOSE CONFIG

79 Num Shots: 4

CONTROL & LOGIC > AUTORECLOSE CONFIG > P/F SHOTS

79 P/F Prot'n Trip 1: Inst

79 P/F Prot'n Trip 2: Inst

79 P/F Prot'n Trip 3 : Delayed

79 P/F Prot'n Trip 4: Delayed

79 P/F Delayed Trips to Lockout: 3

CONTROL & LOGIC > AUTORECLOSE CONFIG > SEF SHOTS

79 SEF Prot'n Trip 1: Delayed

79 SEF Prot'n Trip 2: Delayed

79 SEF Delayed Trips to Lockout: 3

Note that Instantaneous' trips are inhibited if the shot is defined as 'Delayed'

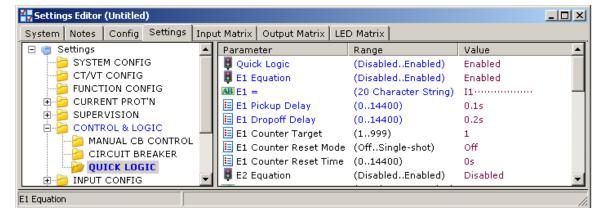

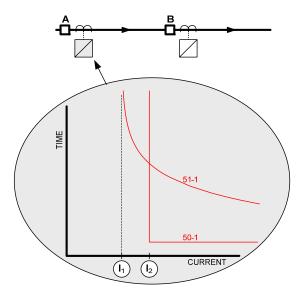

## 4.1.2 Auto-Reclose Example 2 (Use of Quicklogic with AR)

Figure 4.1-2 Example of Logic Application

Requirement: The relay at location 'A' is required to provide a reclose sequence of 2 Instantaneous followed by 2 delayed recloses. Where the fault current level is between the values '11' and '12' and the first trip is initiated from the 51-1 (IDMT) element, the IDMT characteristic should trip the CB and lockout the auto-reclose.

Typical settings are:

CONTROL & LOGIC > AUTORECLOSE PROT'N:

79 P/F Inst Trips: 50-1

79 P/F Delayed Trips: 51-1

CONTROL & LOGIC > AUTORECLOSE CONFIG > P/F SHOTS

79 P/F Prot'n Trip 1 : Inst 79 P/F Prot'n Trip 2 : Inst

79 P/F Prot'n Trip 3: Delayed 79 P/F Prot'n Trip 4: Delayed

The above settings are suitable at values of fault current above '12' however were a fault to occur with a current value between '11' and '12' this would be detected by the 51-1 element only. As **Prot'n Trip 1** = **Inst** then the relay would trip and reclose whereas it is required to lockout for this occurrence.

To provide a lockout for the above faults an additional element 50-2 with identical settings to 50-1 is assigned as a Delayed Trip and is used in conjunction with the Quick Logic feature i.e.

OUTPUT CONFIG>OUTPUT MATRIX: 51-1 = V1

OUTPUT CONFIG>OUTPUT MATRIX: 50-2 = V2

OUTPUT CONFIG>OUTPUT MATRIX: E1 = V3

CONTROL & LOGIC>QUICK LOGIC: E1 = V1.!V2

INPUT CONFIG>INPUT MATRIX: 79 Lockout = V3

# 4.2 Quick Logic Applications

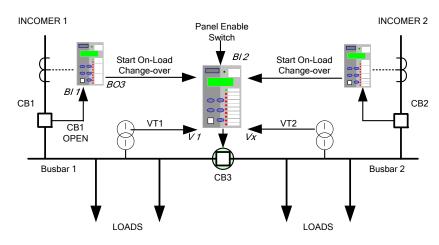

## 4.2.1 Auto-Changeover Scheme Example

Figure 4.2-3 Example Use of Quick Logic

The MV installation illustrated above is fed from two incomers. To limit the substation fault level the busbar is run with CB3 open. When a fault occurs on one of the incomers it is isolated by the circuit protection. To re-supply the disconnected loads from the remaining incomer CB3 is closed.

If the line fault occurs on incomer 1 it must be confirmed that CB 1 has opened before CB3 can be closed. The relay on incomer 1 confirms that a trip has been issued to CB1 (e.g. Binary Output 2), that CB 1 has opened (e.g. Binary Input 1) and that no current flows in the circuit (e.g. 37-1 = Virtual 1):

#### Incomer 1 Relay is Configured:

CB1 Open auxiliary switch wired to BI 1

Trip output to CB1 = BO 2

OUTPUT CONFIG>OUTPUT MATRIX: 37-1 = V1

OUTPUT CONFIG>OUTPUT MATRIX: E1 = BO3

CONTROL & LOGIC>QUICK LOGIC: E1 = O2.I1.V1

The output from Incomer 1 (Binary Output 3) relay is input to the relay on CB 3 (Binary Input 1). A panel switch may be used to enable the On-Load Change-over scheme (Binary Input 2). Before Closing CB3 a check may be made that there is no voltage on busbar 1 (27/59-1 = Virtual 1). CB 3 is closed from Binary Output 3.

#### CB3 Relay is Configured:

Panel switch (ON-Load Change-over Enabled) wired to BI2

OUTPUT CONFIG>OUTPUT MATRIX: 27/59-1 = V1

OUTPUT CONFIG>OUTPUT MATRIX: E1 = BO3

CONTROL & LOGIC>QUICK LOGIC: E1 = I1.I2.V1

If required a time delay can be added to the output using the CONTROL & LOGIC > QUICK LOGIC: *E1 Pickup Delay* setting.

## **Section 5: Supervision Functions**

## 5.1 Circuit-Breaker Fail (50BF)

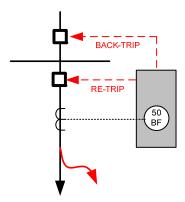

Where a circuit breaker fails to operate to clear fault current the power system will remain in a hazardous state until the fault is cleared by remote or back-up protections. To minimise any delay, CB Failure protection provides a signal to either re-trip the local CB or back-trip 'adjacent' CBs.

The function is initiated by the operation of user selectable protection functions or from a binary input. Current flow is monitored after a tripping signal has been issued if any of the 50BF current check elements have not reset before the timers have expired an output is given. For CB trips where the fault is not current related an additional input is provided (50BF Mech Trip) which monitors the CB closed input and provides an output if the circuit breaker has not opened before the timers expire.

The relay incorporates a two-stage circuit breaker fail feature. For some systems, only the first will be used and the CB Failure output will be used to back-trip the adjacent CB(s). On other systems, however, this output will be used to re-trip the local CB to minimise potential disruption to the system; if possible via a secondary trip coil and wiring. The second CB Failure stage will then be used to back-trip the adjacent CB(s).

If the CB is faulty and unable to open, a faulty contact can be wired to the CB faulty input of the relay and if a trip occurs while this input is raised the CB fail delay timers may be by-passed to allow back tripping to occur without delay.

Figure 5.1-1 Circuit Breaker Fail

#### 5.1.1 Settings Guidelines

#### 50BF Setting

The phase current setting must be set below the minimum protection setting current.

#### 50BF Setting-I4

The EF or SEF current setting must be set below the minimum protection setting current.

#### 50BF Ext Trig

Any binary input can be mapped to this input to trigger the circuit breaker fail function. Note current must be above setting for the function to operate.

#### 50BF Mech Trip

Any binary input can be mapped to this input to trigger the circuit breaker fail function. Note for the function to operate the circuit breaker closed input is used to detect a failure, not the current.

#### 50BF CB Faulty

Any binary input can be mapped to this input, if it is energised when a trip initiation is received an output will be given immediately (the timers are by passed).

#### 50BF DTL1/50BF DTL2

Busbar tripping scheme.

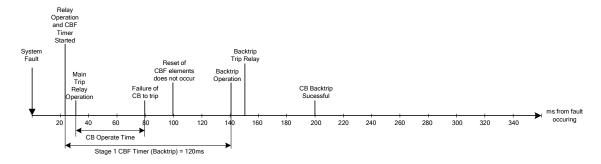

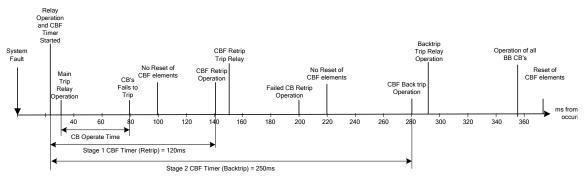

The time delays run concurrently within the relay. The time delay applied to the CB Fail protection must be in excess of the longest CB operate time + relay reset time + a safety margin.

| First Stage (Retrip)                      |       |

|-------------------------------------------|-------|

| Trip Relay operate time                   | 10ms  |

| Reset Time                                | 20ms  |

| CB Tripping time                          | 50ms  |

| Safety Margin                             | 40ms  |

| Overall First Stage CBF Time Delay        | 120ms |

|                                           |       |

| Second Stage (Back Trip)                  |       |

| First CBF Time Delay                      | 120ms |

| Trip Relay operate time                   | 10ms  |

| CB Tripping time                          | 50ms  |

| Reset Time of measuring element           | 20ms  |

| Margin                                    | 60ms  |

| Overall Second Stage CBF Time Delay 260ms |       |

The safety margin is extended by 1 cycle for the second CBF stage as this will usually involve a back-trip of a

The timing sequence for each stage of the circuit breaker fail function is as below.

Figure 5.1-2 Single Stage Circuit Breaker Fail Timing

Figure 5.1-3 Two Stage Circuit Breaker Fail Timing

## 5.2 Current Transformer Supervision

When a CT fails, the current levels seen by the protection become unbalanced, however this condition would also occur during a system fault. Depending upon the relay model different methods are used to determine the condition, depending upon the measured quantities available.

#### Current Transformer Supervision (60CTS - 7SR11)

Following a CT Failure, if one or two of the three phases falls below the CT supervision setting the element will operate

Operation is subject to a time delay to prevent operation for transitory effects.

A 3-phase CT failure is considered so unlikely (these being independent units) that this condition is not tested for.

#### Current Transformer Supervision (60CTS - 7SR12)

When a CT fails, the current levels seen by the protection become unbalanced. A large level of NPS current is therefore detected - around 0.3 x In for one or two CT failures. However this condition would also occur for a system fault. To differentiate between the two conditions, the element uses NPS voltage to restrain the CTS algorithm as shown in the accompanying table.

| NPS Current | NPS Voltage | Decision     |

|-------------|-------------|--------------|

| > Setting   | > Setting   | System Fault |

| > Setting   | < Setting   | CT Failure   |

Table 5-1 Determination of VT Failure (1 or 2 Phases)

Following a CT Failure, there should be little or no NPS voltage. Perhaps 0.1 x Vn as a maximum.

Operation is subject to a time delay to prevent operation for transitory effects.

A 3-phase CT failure is considered so unlikely (these being independent units) that this condition is not tested for.

# 5.3 Voltage Transformer Supervision (60VTS)

Although VTs rarely fail themselves, VT Supervision presents a common application because of the failure of protective Fuses connected in series with the VTs.

When a VT failure occurs on one or two phases, the voltage levels seen by the protection become unbalanced. A large level of NPS voltage is therefore detected - around 0.3 x Vn for one or two VT failures. However this condition would also occur for a system fault. To differentiate between the two conditions, the element uses NPS current to restrain the VTS algorithm as show in the accompanying table.

| NPS Voltage | NPS Current | Decision     |

|-------------|-------------|--------------|

| > Setting   | > Setting   | System Fault |

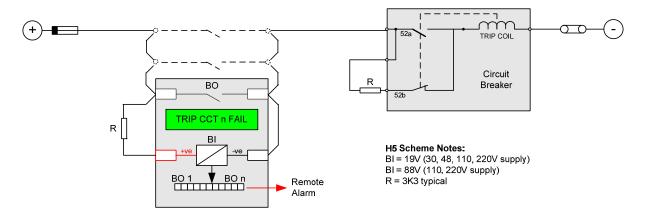

| > Setting   | < Setting   | VT Failure   |